# **Learning Outcome**

#### Able to:

Analyze a simplified BJT Op-amp circuit.

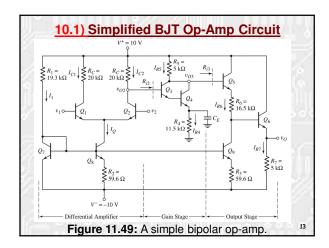

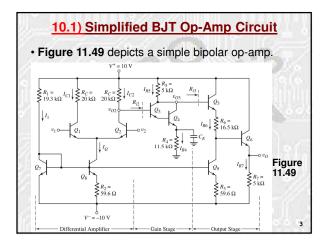

#### 10.1) Simplified BJT Op-Amp Circuit (Cont)

- Simplified analysis and design → only resistive loads are considered.

- · Diff-amp is biased with Widlar current source.

- · One-sided output of diff-amp is connected to Darlington pair gain stage.

- Bypass capacitor  $C_E$  is included to increase smallsignal voltage gain.

- · Output stage is an emitter follower.

- · Generally, wanted the dc value of the output voltage  $v_0 = 0$  when input voltage =  $0 \rightarrow$  insert dc level shifting circuit between  $v_{03}$  and  $v_0$ .

## 10.2) DC Characteristics

### **Example 11.15**

Analyze the dc characteristics of BJT op-amp circuit. Neglect base currents. Assume  $V_{RE}(\mathbf{on}) = 0.7 \text{V}$  for all transistors except  $Q_8$  and  $Q_9$  in Widlar.

- Reference current  $I_1$ :  $I_1 = \frac{10 0.7 (-10)}{19.3} = 1 \text{mA}$

- Bias current Io (from Widlar):

$$I_{Q}R_{2} = V_{T} \ln \left(\frac{I_{1}}{I_{Q}}\right) \Rightarrow I_{Q} = 0.4 \text{ mA}$$

· Collector currents:

$I_{CI} = I_{C2} = I_{Q} / 2 = 0.2 \text{ mA}$

## 10. 2) DC Characteristics (Cont)

$$\begin{array}{ll} \bullet \ \mathsf{DC} \ \mathsf{voltage} \ \mathsf{at} \ \mathsf{collector} \ Q_2 \\ V_{O2} = \mathbf{10} \bullet I_{C2} \ R_C = 10 - (0.2\mathrm{m})(20\mathrm{k}) \\ \Leftrightarrow V_{O2} = 6\mathrm{V} = v_{cm}(\mathbf{max}) \end{array}$$

• Common-mode input range:  $-8.6V \le v_{cm} \le 6V$  $v_{cm}(min) = -10 + V_{BE8} + V_{BEI}$  (ignoring  $I_0R_2$ )

$\bullet$  Values for  $I_{R4}$  and  $I_{R5}$ :

$$I_{R4} = \frac{V_{O2} - 2V_{BE}(\text{on})}{R_A} = \frac{6 - 1.4}{11.5 \text{k}} = 0.4 \text{mA}$$

$I_{R5} \approx I_{R4} = 0.4 \text{ mA}$  (neglecting base currents)

### 10. 2) DC Characteristics (Cont)

- DC voltage at collectors of  $Q_3$  and  $Q_4$

- $V_{O3} = 10 I_{R5}R_5 = 10 (0.4\text{m})(5\text{k})$

- $V_{03}$  = 8V is midway between 10V supply voltage and 6V dc input voltage  $(V_{o2}) \rightarrow$  This allows a maximum symmetrical swing for time-varying  $v_{o3}$

- DC voltage level shifting by  $Q_5$  and  $R_6$ :

$I_{R6} = I_Q = 0.4$  mA, since  $R_3 = R_2$   $V_{B6} = V_{O3} - V_{BE}$ (on) -  $I_{R6}R_6 = 8$ -0.7-(0.4m)(16.5k)

- $V_{B6} = 0.7 \text{ V}$  produces a zero dc output at  $v_0$ (emitter of  $Q_6$ ) for a zero diff-mode input voltage.

- Current  $I_{R7}$ :  $I_{R7} = \frac{v_O (-10)}{R_7} = \frac{10}{5k} = 2\text{mA}$

# 10. 3) AC Characteristics

#### Example 11.16

Determine small-signal diff-mode voltage gain, A, Use Fig 11.49. Transistor parameters:  $\beta = 100$ ,  $V_A = \infty$ .

Overall differential-mode gain:

$$A_{d} = A_{d1}.A_{2}.A_{3} = \left(\frac{v_{o2}}{v_{1} - v_{2}}\right) \left(\frac{v_{o3}}{v_{o2}}\right) \left(\frac{v_{o}}{v_{o3}}\right)$$

- A valid only if load resistance of following stages are considered in the calculation:

- $\rightarrow R_{i2}$ : input resistance to Darlington pair.

- $\rightarrow R_{i3}$ : input resistance to output stage.

## 10. 3) AC Characteristics (Cont)

· One-sided diff-mode voltage gain of diff-amp:

$$A_{d1} = \left(\frac{V_{o2}}{v_d}\right) = \frac{g_m}{2} (R_C || R_{i2})$$

$r_{\pi 4} = \beta V_T / I_{R4} = (100)(0.026) / 0.4 \text{m} = 6.5 \text{k}\Omega$

$r_{\pi^3} \cong \beta^2 V_T / I_{R4} = (100)^2 (0.026) / 0.4 \text{m} = 650 \text{k}\Omega$

$R_{i2} = r_{\pi 3} + (1 + \beta)r_{\pi 4} = 650k + (101)(6.5k) = 1307k\Omega$

$g_m = I_O/(2V_T) = 0.4 \text{m}/(2 \times 0.026) = 7.70 \text{mA/V}$

$A_{d1} = (7.70 \text{ m/2})(20 \text{ k} \| 1307 \text{ k}) = 75.8$

$\rightarrow$  Since load resistance  $R_{i2} >> R_C$ , there is no significant loading effect of 2<sup>nd</sup> stage on diff-amp.

#### 10. 3) AC Characteristics (Cont)

• The voltage gain of the Darlington pair:

$$A_2 = \frac{I_{R4}}{2V_T} (R_5 || R_{i3})$$

$r_{\pi 5} = \beta V_T / I_{R6} = (100)(0.026) / 0.4 \text{m} = 6.5 \text{k}\Omega$

$$r_{\pi 6} = \beta V_T / I_{R7} = (100)(0.026) / 2m = 1.3k\Omega$$

$$R_{i3} = r_{\pi 5} + (1 + \beta)[R_6 + r_{\pi 6} + (1 + \beta)R_7] = 52.8 \text{M}\Omega$$

Since  $R_{i3} >> R_5$ , the output stage does not load down the gain stage, and small-signal voltage gain is approximately

$$\therefore A_2 \cong \frac{I_{R4}}{2V_T} (R_5) = \frac{0.4 \,\text{m}}{2(0.026)} (5 \,\text{k}) = 38.5$$

10

## 10. 3) AC Characteristics (Cont)

• The combination of  $Q_5$  and  $Q_6$  forms an emitter follower, and the gain of the output stage is:

$$A_3 = v_o / v_{o3} \cong 1$$

• The overall small-signal voltage gain is therefore:

$$A_d = A_{d1}.A_2.A_3 = 75.8 \times 38.5 \times 1 = 2918$$

Larger circuits