# COLLEGE OF ENGINEERING PUTRAJAYA CAMPUS FINAL EXAMINATION

# SEMESTER 2 2018 / 2019

| PROGRAMME    | : Bachelor of Electrical & Electronics Engineering (Honours)<br>Bachelor of Electrical Power Engineering (Honours) |

|--------------|--------------------------------------------------------------------------------------------------------------------|

| SUBJECT CODE | : EEEB273/EEEB2014                                                                                                 |

| SUBJECT      | : ELECTRONIC ANALYSIS AND DESIGN II                                                                                |

| DATE         | : January/February 2019                                                                                            |

| TIME         | : 3 hours                                                                                                          |

# **INSTRUCTIONS TO CANDIDATES:**

- 1. This paper contains **FIVE** (5) questions in **TEN** (10) pages.

- 2. Answer ALL questions.

- 3. Write all answers in the answer booklet provided. Use pen to write your answer.

- 4. Write answer to different question on **a new page**.

# THIS QUESTION PAPER CONSISTS OF TEN (10) PRINTED PAGES INCLUDING THIS COVER PAGE.

#### Question 1 [20 marks]

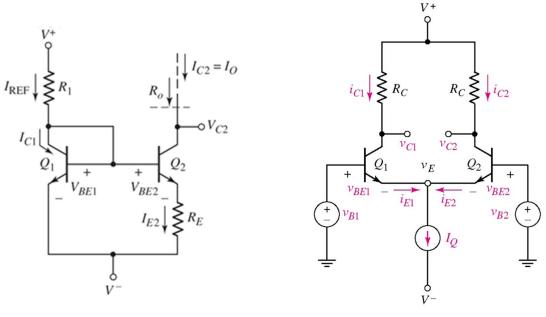

(a) An **npn** current source is shown in **Figure 1**. The transistor parameters are  $\beta = 200$ ,  $V_{BE}(\text{on}) = 0.7 \text{ V}$ , and  $V_A = 250 \text{ V}$ . The required **output current** is 20  $\mu$ A and the **reference current** is 0.5 mA. Calculate the percentage change in output current  $I_O$  when  $V_{C2}$  changes from 0.9 to 5 V. [8 marks]

Figure 1

- (b) A BJT differential amplifier with passive load is shown in Figure 2. The power supplies are  $V^+ = 5$  V and V = -5 V. Draw a pnp version of the circuit. [4 marks]

- (c) For the **pnp** differential amplifier drawn in **part** (b), the value of  $I_Q = 0.5$  mA. It is required that when  $v_{B1} = v_{B2} = 0$  V, the voltage  $V_{EC1} = V_{EB}(on) = 0.7$  V. Let  $\beta = 200$  and  $V_A = \infty$  and **neglect the base currents**. Calculate the maximum value of load resistance  $R_C$  for this condition and the one-sided differential gain,  $A_d$ . [8 marks]

# Question 2 [20 marks]

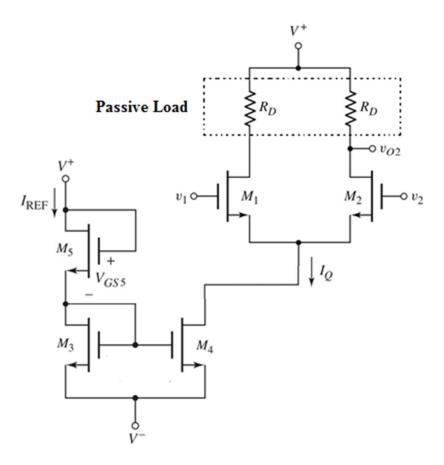

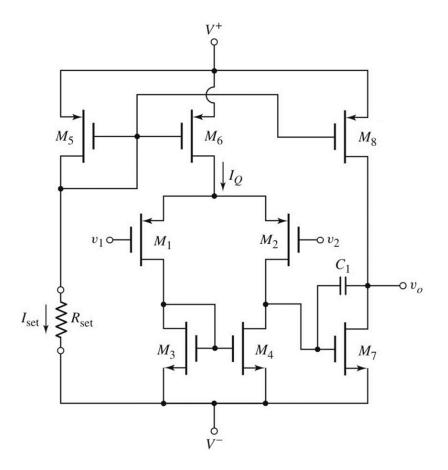

Figure 3 shows an N-MOSFET differential amplifier with passive load. The differential amplifier is biased by an N-MOSFET current source constructed by using  $M_3$ ,  $M_4$ , and  $M_5$  that produces the bias current  $I_Q = 0.20$  mA. Study the Figure 3 carefully. The overall circuit is powered by  $V^+ = 5$  V and  $V^- = -5$  V, with  $R_D = 40$  k $\Omega$ . Take note that different values of parameters for MOSFET transistors are used in part (a) and part (c) of this Question 2.

- (a) For the N-MOSFET current source bias circuit in the Figure 3 the transistors parameters are  $V_{TN} = 0.5$  V,  $k'_n = 50 \ \mu A/V^2$ ,  $(W/L)_3 = (W/L)_4 = 15$ ,  $(W/L)_5 = 3$ , and  $\lambda_n = 0$ . Calculate the value of  $V_{GS5}$ . [5 marks]

- (b) The differential amplifier with passive load shown in Figure 3 is to be redesigned to increase its differential-mode voltage gain  $(A_d)$  by replacing its passive load  $(R_D)$  with an active load constructed using a P-MOSFET Cascode current source. Draw the new

circuit for the differential amplifier incorporating the active load's full circuit diagram. Label the new circuit correctly and clearly with appropriate symbols and numbering for the P-MOSFET transistors used in the new circuit starts from  $M_7$ . You are NOT required to draw the N-MOSFET current source that biased the differential amplifier in the Figure 3. [5 marks]

(c) For the differential amplifier circuit in the Figure 3 and the new circuit with P-MOSFET active load in part (b), assume that N-MOSFET and P-MOSFET devices are available with parameters shown in Table 1. For the circuit in Figure 3, given  $R_D = 40 \text{ k}\Omega$ . Determine how much the differential-mode voltage gain ( $A_d$ ) of the differential amplifier had increased when the active load is used to replace the passive load in the differential amplifier in Figure 3. [10 marks]

| N-MOSFET transistor               | <b>P-MOSFET</b> transistor        |

|-----------------------------------|-----------------------------------|

| $K_n = 0.4 \text{ mA}/V^2$        | $K_p = 0.2 \text{ mA}/V^2$        |

| $V_{TN} = 0.5 \text{ V}$          | $V_{TP} = -1 \text{ V}$           |

| $\lambda_n = 0.02 \text{ V}^{-1}$ | $\lambda_p = 0.02 \text{ V}^{-1}$ |

**Table 1: MOSFET parameters**

# Question 3 [20 marks]

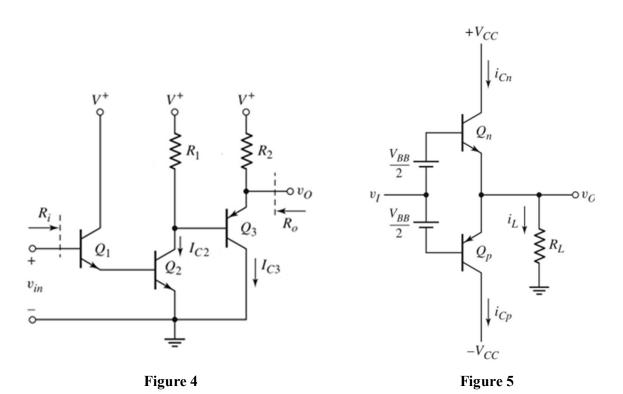

(a) For circuit in Figure 4, given that  $I_{C2} = 1.2 \text{ mA}$ ,  $I_{C3} = 5 \text{ mA}$ ,  $R_1 = 50 \text{ k}\Omega$ , and  $R_2 = 5 \text{ k}\Omega$ . Determine the input resistance ( $R_i$ ) and output resistance ( $R_o$ ) of the circuit. Let the transistor parameters  $\beta = 60$  and  $V_A = \infty$ . [10 marks]

- (b) **Compare and contrast** the Class-A with Class-B, Class-B with Class-AB, a

- (b) Compare and contrast the Class-A with Class-B, Class-B with Class-AB, and Class-A with Class-AB output stages, respectively. [2 marks]

- (c) For the Class-AB output stage given in Figure 5,  $V_{CC} = 10$  V,  $V_{BB} = 1.35$  V,  $R_L = 100 \Omega$ , and for the transistors  $I_S = 10^{-13}$  A. For an output voltage  $v_0 = 5$  V, calculate  $i_{cn}$ ,  $i_{cp}$  and the power dissipated in both  $Q_n$  and  $Q_p$  transistors. [8 marks]

# Question 4 [20 marks]

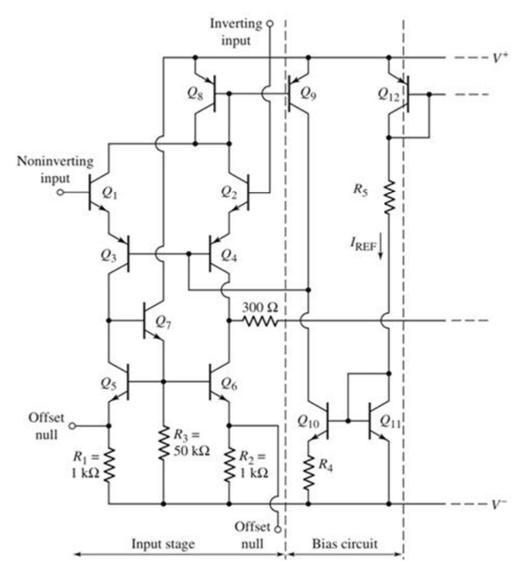

- (a) Consider the bias circuit portion of the 741 op-amp in Figure 6. Assume that the transistor parameters of  $I_s = 5 \times 10^{-16}$  A. The bias voltages are given as  $\pm 15$  V. Neglect the base currents.

- (i) Redesign the bias circuit to obtain  $I_{REF} = 0.4$  mA and  $I_{C10} = 40 \ \mu$ A. [4 marks]

- (ii) Determine the values of  $V_{EB12}$ ,  $V_{BE11}$ , and  $V_{BE10}$ . [6 marks]

Figure 6

(b) Consider the MC14573 op-amp in Figure 7. Assume transistor parameters of  $V_{TN} = 0.5 \text{ V}$ ,  $V_{TP} = -0.5 \text{ V}$ ,  $K_n = 125 \text{ }\mu\text{A}/\text{V}^2$ ,  $K_p = 100 \text{ }\mu\text{A}/\text{V}^2$ ,  $\lambda_n = 0.01 \text{ }\text{V}^{-1}$ , and  $\lambda_p = 0.02 \text{ }\text{V}^{-1}$ . Given that bias current for differential amplifier is  $I_Q = 0.1 \text{ }\text{mA}$ .

**Determine** the **overall small signal differential-mode voltage gain** for the **MC14573** opamp in the **Figure 7**. <u>Value for gain of the output stage</u> consists of transistor  $M_7$  and  $M_8$  is given by equation  $A_{v2} = g_{m7}(r_{o7} \parallel r_{o8})$ . [10 marks]

Figure 7

# Question 5 [20 marks]

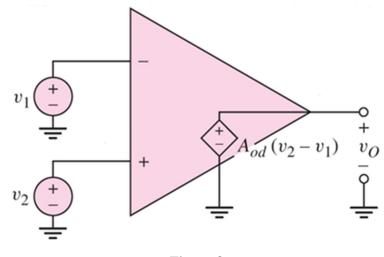

- (a) The equivalent circuit of an ideal operational amplifier (**op-amp**) is given in **Figure 8**.

- (i) **Explain** why the op-amp input currents are zero. [1 mark]

- (ii) **Explain** the **'virtual short'** concept for the ideal op-amp. [3 marks]

Figure 8

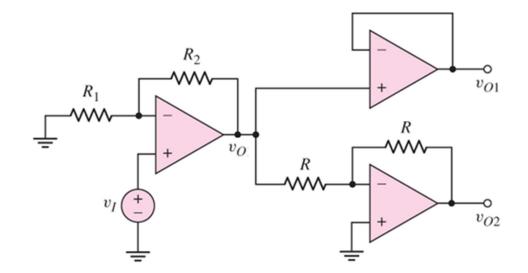

(b) Figure 9 shows a cascade circuit implemented using ideal op-amps. Determine the voltages  $v_0$ ,  $v_{01}$  and  $v_{02}$ . Given  $R = 10 \text{ k}\Omega$ ,  $R_1 = 20 \text{ k}\Omega$ ,  $R_2 = 30 \text{ k}\Omega$ , and  $v_I = 1 \text{ mV}$ .

[4 marks]

Figure 9

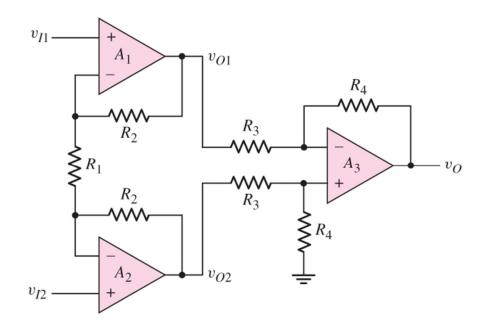

(c) Refer to the **instrumentation amplifier** in **Figure 10**. With proper analysis using ideal operational amplifier characteristics, it can be found that:

$$v_{O} = \frac{R_{4}}{R_{3}} \left( 1 + \frac{2R_{2}}{R_{1}} \right) \left( v_{I2} - v_{I1} \right)$$

Resistor  $R_1$  is such that it consists of a fixed resistor  $R_{1f}$  in series with a potentiometer  $R_{1\nu}$ . Design the circuit such that the differential gain varies between 10 to 500 V/V. Set the difference amplifier gain to 4. The maximum current in  $R_1$  is limited to 10  $\mu$ A for a maximum output voltage of 5 V. What value of potentiometer  $(R_{1\nu})$  is required?

[12 marks]

Figure 10

# -END OF QUESTION PAPER-

# **APPENDIX:**

#### A) BASIC FORMULA FOR TRANSISTOR

BJT **MOSFET**  $i_C = I_S e^{v_{BE}/V_T}$ ; NPN ; N-MOSFET  $v_{DS}(\text{sat}) = v_{GS} - V_{TN}$  $i_C = I_S e^{v_{EB}/V_T}$ ; PNP  $i_D = K_n [v_{GS} - V_{TN}]^2$  $i_C = \beta i_B = \frac{\beta}{\beta + 1} i_E$  $K_n = \frac{\mu_n C_{ox} W}{2I} = \frac{k_n}{2} \cdot \frac{W}{I}$  $i_E = i_B + i_C$ ; P-MOSFET  $v_{SD}(\text{sat}) = v_{SG} + V_{TD}$ ;Small signal  $i_D = K_p [v_{SG} + V_{TP}]^2$  $\beta = g_m r_{\pi}$  $K_{p} = \frac{\mu_{p}C_{ox}W}{2I} = \frac{k_{p}}{2} \cdot \frac{W}{I}$  $g_m = \frac{I_{CQ}}{V_m}$ ;Small signal  $r_{\pi} = \frac{\beta V_T}{I_{CO}}$  $g_m = 2\sqrt{K_n I_{DQ}}$ ; N – MOSFET  $g_m = 2\sqrt{K_p I_{DQ}}$ ; P-MOSFET  $r_o = \frac{V_A}{I_{CO}}$  $r_o \cong \frac{1}{\lambda I_{po}}$  $V_{T} = 26 \, {\rm mV}$

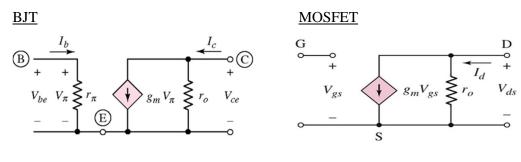

# B) <u>HYBRID- EQUIVALENT CIRCUITS</u>

C) QUADRATIC FORMULA

$$Ax^{2} + Bx + C = 0 \qquad \rightarrow \quad x = \frac{-B \pm \sqrt{B^{2} - 4AC}}{2A}$$